2024.12.19 半導体設計の進化とエコシステム最新動向

セミコンジャパン2024でのセミナーにはシノプシス、アンシス、図研、ケイデンスのほか、mathworksとシーメンスも登壇した

半導体の高性能化が進む中、設計・開発から製造に関わる全ての工程は複雑化している。設計・開発を支える電子設計自動化(EDA)ツールも進化を遂げるとともに、EDA各社のビジネスモデルや事業環境にも変化が起こっている。EDAとは集積回路や電子機器の設計・開発の自動化を支援するソフトウエアやハードウエアの総称。設計には複数の階層が存在し、これまでは階層ごとに開発が進められてきた。しかし、EDAベンダーの中で今、M&Aや協業を通じて統合的なエコシステム形成を進める動きがある。

半導体設計の分類

EDAツールを使用する設計は①前工程でウエハーに書き込む集積回路の設計②後工程でのパッケージングや電極形成の設計③製造後のプリント配線板へのデバイス配置設計―という3つの階層に分けられる。それぞれの設計で使用するソフトウエアやツールも異なり、供給するEDAベンダーも異なる。

設計分野の動向

より高性能の電子機器をより高密度化・小型化するため、集積回路設計では回路線幅の微細化を追求し、プリント配線板設計ではチップや電子部品の効率的な配置・配線を目指すのが一般的。近年、回路線幅の微細化には莫大な投資が必要となっており、プリント配線板には実装面積の制約があるため、後工程での設計の重要性が増している。複数のチップを1チップにまとめる「チップレット」や3次元実装が注目を集めており、パッケージング設計における高い精度が求められている。

こうした動きを背景に、設計の一貫性を確保するため、これまで各階層で分断されていた設計をつなぐ動きが出てきた。その橋渡しを担うのがEDAベンダーだ。

この動向は半導体業界全体でも注目を集めている。今月13日まで東京ビッグサイトで開催された半導体製造に関する国際展示会「セミコンジャパン2024」では、今年から設計・開発分野に特化したイベント「ADIS(Advanced Design Innovation Summit)を併催。主要EDAベンダーが一堂に会するセミナーも行われた。

シノプシスは図研と協業

米国の大手EDAベンダーで集積回路設計のソリューションを手掛けるシノプシスは企業連携により各階層をつなぐ。パッケージングとプリント配線板の設計ツールを提供する国内ベンダー図研と協業しているほか、半導体設計の解析ソフトウエアを扱う米国のアンシスの買収を発表しており、3社のツールを組み合わせることで統合的な半導体・電子機器設計が可能になるソリューションを提供している。3社はADISで共同のブースを出展、アライアンスを強調した。

具体的には、シノプシスのチップレット設計ツール「3DIC Compiler」と図研のマルチボード設計環境「CR-8000 Design Force」を連携させる。それぞれの設計を相互にやり取りしながら行えるよう、共通プラットフォームを開発・提供する。アンシスのソリューションは、2社のツールで設計したものをシミュレーションできる。

ケイデンスは自社内でパッケージまで設計可能

集積回路設計ツールの大手ベンダーの一角である米ケイデンス・デザイン・システムズは、集積回路設計からパッケージ設計まで一貫して行うことができる統合的なソリューションを提供している。同社が提供する「Integrity 3D-ICプラットフォーム」は解析や協調設計が可能。これまでのM&Aによるさまざまな設計分野の統合を通じて実現した。

複雑化する最先端半導体を安定的かつ効率的に製造していくためにEDAは欠かせない。EDA各社は新たな取り組みを通じて、半導体の技術革新を支えている。

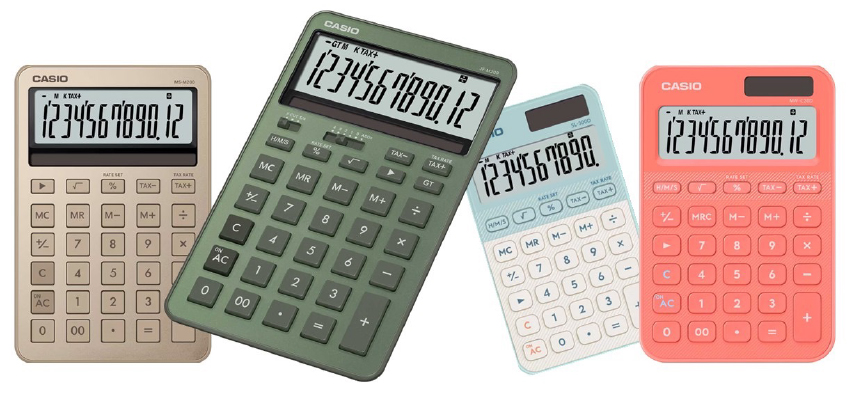

カシオ計算機 8年ぶりの刷新 デザイン電卓15色登場

カシオ計算機 8年ぶりの刷新 デザイン電卓15色登場