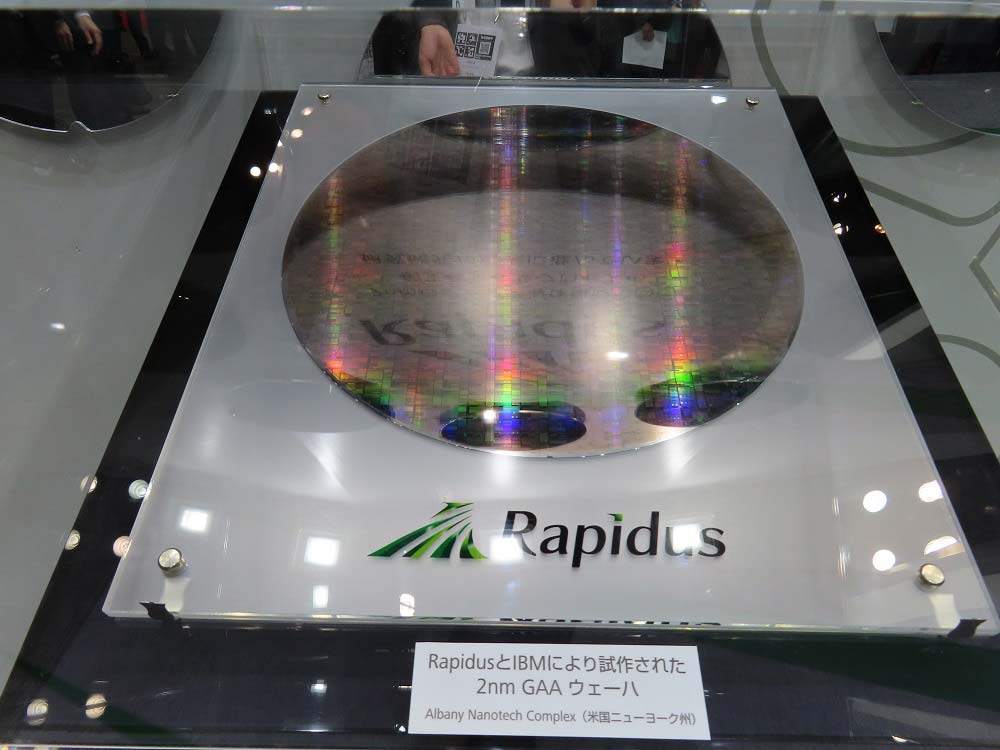

2024.12.12 ラピダス、最先端半導体製造の実現に向けて設計・開発トップ2社と協業

ラピダスとIBMによる2nm GAAウエハーの試作品

ラピダスは日本国内での先端ロジック半導体製造に向け、新たな協業を開始する。11日、米国の電子設計自動化(EDA:Electronic Design Automation)大手であるケイデンス・デザイン・システムズ(以下、ケイデンス)とシノプシスの2社との協業を発表。半導体の設計分野で多くのソリューションを有する2社と協業することで、2ナノメートルクラスの最先端半導体の設計や設計期間の短縮を実現する。

EDAとは

EDAは集積回路や電子機器の設計・開発の自動化を支援するソフトウエアやハードウエアなどの総称。半導体の設計・開発においてはチップの設計から検証、チップ製造で必要となる高度なプロセス設計など幅広く利用される。ケイデンスとシノプシスは、EDAのトップベンダーとして高い世界シェアを誇る。また、半導体には多くのIP(Intellectual Property:知的財産)があり、再設計可能な半導体設計ブロックとしてさまざまな半導体製品の開発に広く利用されている。両社は標準規格のIPからカスタム・アーキテクチャーまで幅広いIPポートフォリオを有し、半導体の設計・開発を支えている。

ケイデンスとは2nm GAAとBSPDN技術実現に向けて

今回、ラピダスとケイデンスが協業するのは、AIにおけるリファレンスデザインとIPポートフォリオの提供に関する事案。ラピダスが目指す2nm GAA(Gate All Around)製造プロセスと裏面電極(BSPDN:Backside Power Delivery Network)技術の設計および製造に対応したケイデンスの設計ソリューションとIPポートフォリオを顧客に提供していく。

ラピダスの小池淳義代表取締役社長は「2nm BSPDN技術におけるケイデンスとの連携により、業界の最前線に立つことになる」と意気込む。GAAとBSPDN技術は今後、ますます厳しくなる低消費電力化および高性能化、さらにSi面積(PPA:Power、Performance、Area)の要件を満たすために必要不可欠になると予想されている。

シノプシスとは、プロセス感度やばらつきの新たなモデル化により設計サイクルタイムを短縮するソリューションを共同開発する。プロセスやプロセス設計キット(PDK:Process Design Kit)の更新に合わせたロジック、メモリーのタイミングモデル作成に必要な時間を従来の2~3カ月から数日へと大幅に短縮できる。

今回の協業の一環としてシノプシスは、AIベースのEDAツール群を活用した最先端設計フローを開発する。ラピダスの2nm GAAプロセス対応の幅広いIPポートフォリオを実現することで、設計と製造を同時に最適化。ラピダスが目指すアジャイル開発のコンセプトを具現化していく。

設計・開発のボトルネック解消へ

半導体設計のサイクルタイムで課題となるのが、IPライブラリーのキャラクタリゼーション。通常はPDKや製造プロセスが更新されるたびにIPのキャラクタリゼーションを行う必要があるため、タイミングモデルを生成するために2~3カ月の期間を要する。共同開発によるソリューションを用いることで、設計サイクルのボトルネックを解消する。

日本国内での先端半導体製造を目指すラピダス。今回の協業を通じて、半導体製造の最上流である設計・開発における技術革新を進め、先端半導体製造の実現に向けと取り組みを加速させる。