2020.03.05 【新技術】東工大など5nm FinFET CMOSプロセスで世界最小の高性能分数分周型クロック回路開発

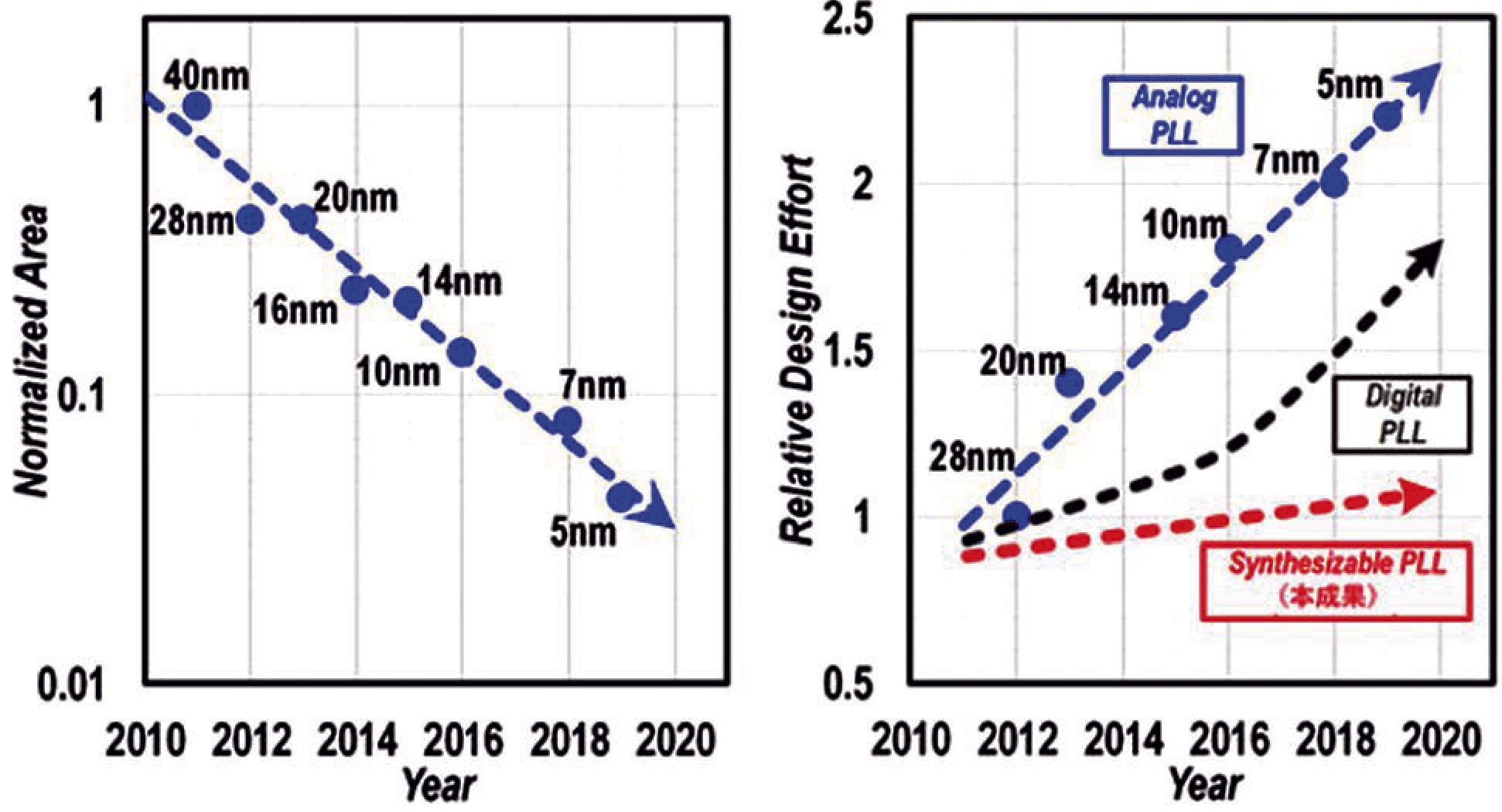

[図1]半導体プロセスのスケーリング(左)とPLL回路設計の難易度(右)

概 要

東京工業大学工学院電気電子系の岡田健一教授らとソシオネクストの研究グループは、最先端の5nm FinFET CMOSプロセスで世界初となる世界最小の高性能分数分周型クロック回路の開発に成功した。この回路はプロセッサやメモリー、通信用のクロック用途として必須の電子回路であり、開発したクロック回路は小型ながらも優れたジッタ特性を持つ。また、細かい周波数調整が可能な分数分周型PLLで構成されており、スペクト... (つづく)

続きは無料会員登録することで

ご覧いただけます。

パイオニア 新体制で始動 次の成長への軌跡を追う

パイオニア 新体制で始動 次の成長への軌跡を追う