2021.07.29 【半導体/エレ商社特集】パッケージング技術ムーアの法則を超越、3D技術でさらなる高性能化

インテルのパッケージング技術開発拠点であるニューメキシコ・リオランチョ工場(提供=インテル)

「半導体のトランジスタ密度は約2年ごとに2倍になる」というムーアの法則が示されてから50年余り。これを支えてきた微細化技術開発は2ナノメートルの領域にまで達した。

「2ナノメートル」はゲート長の長さを示すものではなく、技術の世代を示す符丁のようなもの。数年前から技術の複雑化と高コスト化により、微細化技術の開発は限界に近づいているといわれ、TSMCの微細化ロードマップも2ナノメートルで終了との見方もある。

しかし、人工知能(AI)や5G(第5世代移動通信規格)およびそれ以降の次世代通信、高性能コンピューティング(HPC)などの分野ではさらに高性能、高電力効率、高密度の半導体が求められる。その課題に対応するとして開発が進むのが3Dパッケージング技術だ。

パッケージングは半導体製造における後工程の一部だが、TSMCは「ワークロードの進化により、パッケージング技術はイノベーションの最前線にある。製品の性能、機能、コストに大きな影響を与える」とする。

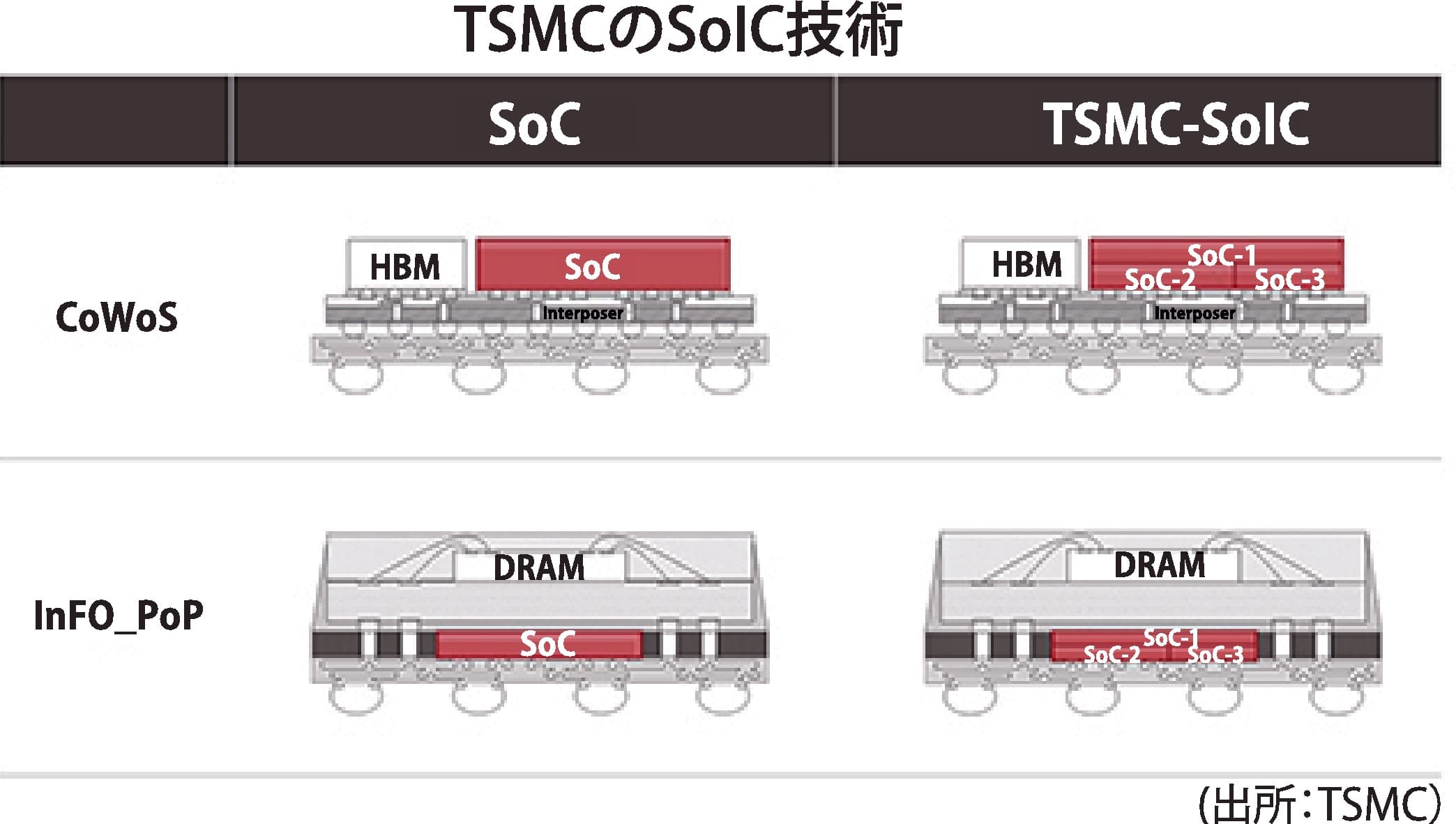

TSMCは昨年、先進の2Dおよび3Dパッケージング技術を提供する「3DFabric」を発表した。先進のロジックシリコンと広帯域メモリー(HBM)を統合し性能と効率向上を実現。またプロセッサーコアとヘテロジニアス(異種混在)チップレットを2D、2.5Dまたは3D実装し、HPCやスマートフォン、IoTエッジデバイスなどに向け小型で多機能のチップを提供する。

3DFabricの中には、ウエハーレベルのファンアウトパッケージング技術(FOWLP)である「InFO」(インテグレーテッド・ファンアウト)や、「CoWoS(チップ・オン・ウエハー・オン・サブストレート)」といったTSMCの従来の後工程パッケージング技術が含まれる。

また、チップスタッキングやウエハースタッキングでシステムを構築する最新の「SoIC(システム・オン・インテグレーテッドチップ)」技術も提供。SoICはさらにCoW(チップ・オン・ウエハー)とWoW(ウエハー・オン・ウエハー)に細分化される。TSMCは2022年までにSoICの量産を開始、同年末までに3DFabric専用の工場を5カ所に設立する計画だ。

AMD、新技術搭載

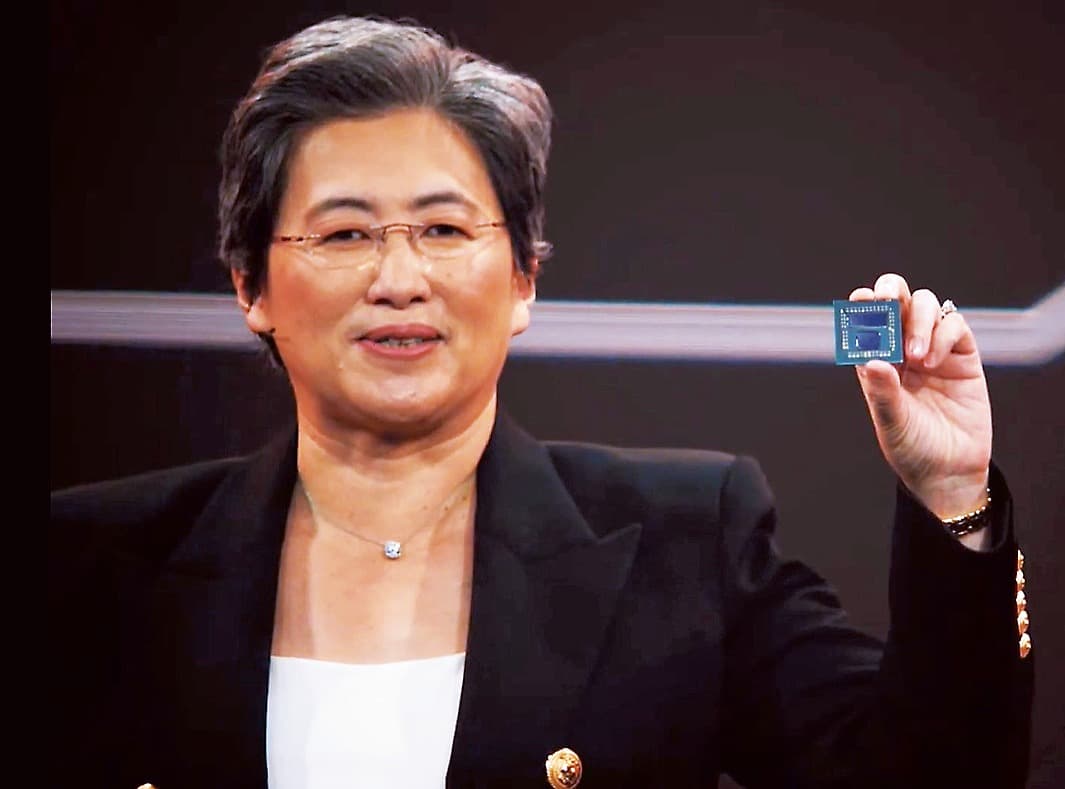

6月1日にオンライン開催された「COMPUTEX(コンピュテックス)台北」で米AMDのリサ・スーCEOは、次世代パッケージング技術「3D V-Cache」を搭載したCPUのプロトタイプを公開、注目を集めた。

同社はTSMCとのパートナーシップを通じ、3Dパッケージング技術開発を続けている。その最初の成果である3D V-Cacheでは、複数コアで構成されるコア・チップレットダイ(CCD)の上に追加のL3キャッシュのダイを縦方向に乗せ、シリコン貫通電極(TSV)で積層する。L3キャッシュはTSMCの7ナノメートルSRAMで容量64メガバイト。追加のL3キャッシュの帯域幅は2テラバイト/秒に達するとしている。

スーCEOが披露したプロトタイプは、自社のCPU「Ryzen9 5900X」をベースとしている。64メガバイトのSRAMを増設したことで各CPUダイのL3キャッシュの容量はオンダイの32メガバイトと合わせ96メガバイトに増量される。パッケージ全体では192メガバイトの大容量キャッシュを搭載でき、従来のRyzen9 5900Xとプロトタイプを比較すると同じコア/スレッド数、同じ動作周波数でゲーム性能が15%向上するという。AMDは今年末までに3D-V CacheによるCPUをリリースする予定だ。

3Dパッケージングではインテルが18年に「Foveros(フォベロス)」を発表、20年に投入されたプロセッサー(開発コード名=Lakefield)で採用している。ロジック回路の上にメモリーをスタッキングするだけでなく、CPU、GPU、AIなどのロジック回路を垂直に積層できる。このほかにも同社は2D、2.5Dのダイスタッキング技術も開発している。

インテルも開発へ

インテルは3月に発表した「IDM2.0」で製造能力拡充と国際競争力強化を強調したが、その成功のカギを握る技術の一つがパッケージングであるとしている。5月上旬にはFoverosや2.5D実装の「EMIB」などの開発・製造拠点であるニューメキシコ州リオランチョの「ファブ11X」への35億ドルの投資を発表した。今年後半に最先端パッケージング技術のための工場を増設する計画だ。

韓国サムスン電子もHPCやAI、大規模データセンターと幅広いアプリケーションに対応するとして2.5D実装技術「インターポーザーCube4」を開発、攻勢をかける。

3D ICは日本の半導体産業復活に向けた切り札でもある。経済産業省は6月、半導体戦略を発表し、国家戦略として半導体のテコ入れを図っていく方針を打ち出した。核となる取り組みの一つが、TSMCが茨城県つくば市に今春設立した「TSMCジャパン3DIC研究開発センター」での3Dパッケージング技術開発。これを日本企業が強みをを持つ素材・製造装置の側面から支援していく。

業界関係者の間では「10年後にはパッケージング技術力が半導体業界の順位を決める」とも言われる。ムーアの法則を超越し、半導体のさらなる性能向上と低消費電力実現に向けた次世代パッケージングへの投資がさらに加速しそうだ。