2022.07.28 【半導体/エレクトロニクス商社特集】 ロジックデバイスの微細化、3ナノメートル時代へサムスンやTSMCなどシノギ、2ナノメートル技術も視野に

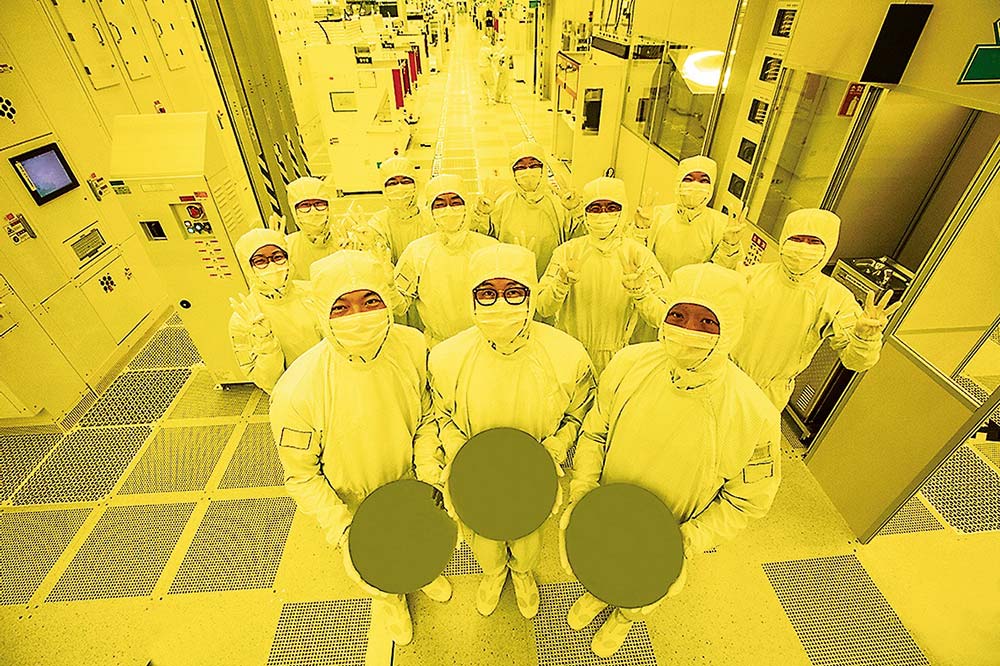

3ナノメートルの量産に着手したサムスン・ファウンドリー

韓国サムスン電子は6月30日、3ナノメートル(ナノは10億分の1)プロセス技術による半導体の量産を開始したと発表した。同社はかねて2022年上半期に3ナノメートルの生産に入ると宣言。だが歩留まりが安定せず、一部では目標達成は不可能との報道もあったが、上半期最後の日に一矢報いた形となった。

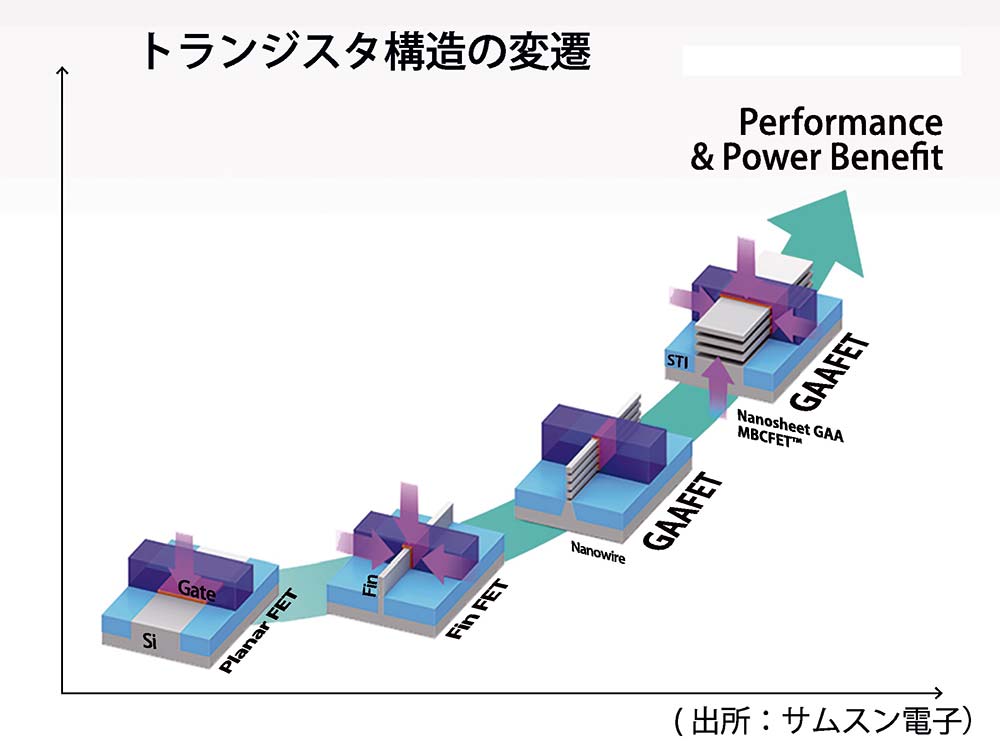

3ナノメートルの量産は世界初だ。微細化の指標となる「ナノメートル」は、プレーナ型FET(電界効果トランジスタ)ではゲート長を表していたが、3次元構造のFinFETが登場してからは、その複雑ゆえ特定の部位の長さを示すものではなく、符号としての意味合いが強くなっている。

とはいえ、微細化でリードする台湾TSMCが今年下半期を予定している3ナノメートルの量産にいち早く着手することは、顧客に技術力をアピールするには十分なインパクトがある。

サムスンの3ナノメートル技術は、次世代のゲートオールアラウンド(GAA)構造のトランジスタを採用する。従来のFinFETアーキテクチャーを採用した5ナノメートル半導体に比べて消費電力を最大45%低減、性能を23%向上させ、実装面積は16%縮小できる。

GAAは電流が流れる4面のチャネルをゲートが完全に取り囲む構造で、電流の流れを 細かく制御するなどチャネルの能力を最大化できる。これによりゲートとチャネルが3面で接する3次元構造FinFETに比べ高い電力効率を実現できる。

GAA構造はナノワイヤを利用してチャネルを構築する手法もあるが、サムスンは紙のように薄く長い「ナノシート」を複数使用してチャネルを構築する「マルチ・ブリッジ・チャネル(MBC)FET」を採用。ナノワイヤベースのGAAトランジスタに比べ、チャネル幅を広くできるため、より性能と電力効率を高めることができるという。

同社は現在、高性能コンピューティング(HPC)向けの生産を開始。今後はモバイル向けSoCなどにも適用していきたい考えだ。また、23年には5ナノメートルプロセスに比べ消費電力を最大50%低減、性能を30%向上、面積を35%小型化させる第2世代「3GAP」、25年にはGAAベースの2ナノメートルプロセス技術をリリースの予定。顧客のニーズに応じた消費電力、性能・面積(PPA)を提供することで、次世代のファウンドリー市場を主導していくと意気込む。

迎え撃つTSMCは、22年下半期にFinFET採用の3ナノメートルプロセス技術「N3」のリリースを予定。N3適用チップを搭載する最初の製品は米アップルのタブレット「iPad」新シリーズになると見られている。当初の月産枚数は3万~3万5000枚の予定だ。

同社は先月、米カリフォルニア州で開催した技術シンポジウムでN3とその改良版である「N3E」プロセスで独自の「FinFLEX」技術を導入することを明らかにした。これは異なるFinFETベースの回路ブロックを一つのチップにまとめるための技術で、高性能を実現する3-2フィン構成のスタンダードセル、高い電力効率とトランジスタ密度を実現する2-1フィン構成、これらの中間に位置する2-2フィン構成の三つの選択肢を提供する。

設計者は必要な性能、電力、ダイサイズの目標に最適化されたフィン構成を実装して、ニーズに合わせたSoCを設計できる。例えばN3Eで3-2フィンを選択した場合、前世代N5に比べ最大33%の性能向上を実現。2-1フィンでは最大36%の面積削減と30%の省電力を実現できるという。

TSMCは25年までに3ナノメートルの派生技術N3E、N3P、N3Xを提供し、25年に次世代2ナノメートル技術「N2」の生産を開始する予定だ。

N2ではナノシートを用いたGAAトランジスタ構造を採用。N3と同じ消費電力で10~15%の性能向上、同じ処理速度で25~30%の省電力を実現するとしている。

この2社を追いかける米インテルは、24年生産開始予定のオングストローム世代の「インテル20A」から「RibbonFET」と呼ぶGAA構造のFETを導入する計画だ。

量産ベースで現行メーンストリームの7ナノメートル、先端分野の5ナノメートルではTSMCが圧倒的優位に立つ。GAAは構造が複雑で、歩留まり率が安定するまで相当の時間を要すると見られる。これを業界に先駆け3ナノメートルで導入するサムスンに分はあるのか、今後の展開が注目される。