2024.01.11 【2024年注目の先端技術特集】湘南工科大渡辺名誉教授 複数入力可能な積層型GAAトランジスタによるNAND、NOR回路の提案 高速性能を維持しつつパターン面積40%に縮小

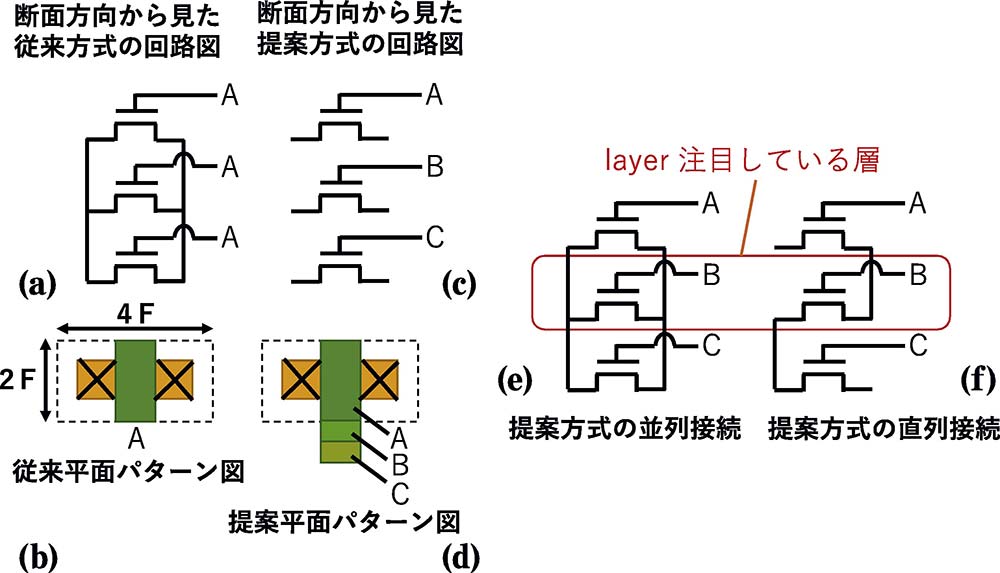

【図1】従来積層型の断面から見た回路図(a)、上面から見た平面パターン図(b)、および提案積層型の断面から見た回路図(c)、上面から見た平面パターン図(d)、提案積層型によるGAAの並列(e)、直列接続(f)

あらまし

複数入力可能な複数入力積層Gate-All-Around(GAA)トランジスタ構造を新たに提案した。8F²(Fはデザインルール)の微細なパターン面積の中に高速低電力なCMOS NAND、NOR回路が実現できることを初めて示した。

ロジックLSIでよく使用される入力数4の場合、過去最少のパターン面積を実現した積層型SGTと比較して高速性能を保持しつつ平面パターン面積を40%... (つづく)

続きは無料会員登録することで

ご覧いただけます。

パイオニア 新体制で始動 次の成長への軌跡を追う

パイオニア 新体制で始動 次の成長への軌跡を追う