2025.10.23 ラムリサーチ、先端半導体パッケージ向け成膜装置、3D ICのゆがみや反りに対応

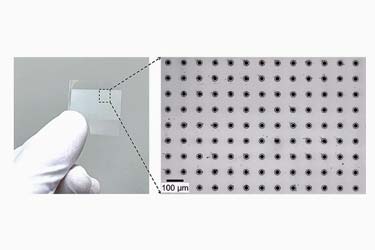

ラムリサーチの3D IC向けダイ間ギャップ埋め込み成膜「VECTOR TEOS 3D」のイメージ

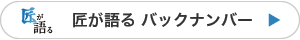

半導体ウエハー製造装置の世界大手、米Lam Research(ラムリサーチ)が、人工知能(AI)や高性能コンピューティング(HPC)向け半導体の先端パッケージングに特化した成膜装置「VECTOR TEOS 3D」を発表した。半導体ダイ(チップ)を垂直方向に積層する3次元集積(3D IC)や機能や性能の異なるダイを一つのパッケージに収めるチップレットなどが対象。ウエハーに生じるゆがみや反りの課題を解決するため、業界最厚かつ均一なダイ間ギャップ埋め込み成膜を行えるとしている。既存製品群VECTOR CoreとTEOSを基盤に構築した。既に世界の主要なロジック、メモリー半導体工場が導入しているという。

AI向け半導体は3D ICやチップレットにより例えば記憶を担うメモリーと演算を担うCPUを近接配置し、電気的な伝送経路を最適化し処理速度を向上させるなどの工夫が進む。しかし、より縦方向に高く、複雑で大きくなるにつれ、製造プロセス中に生じる膜応力によってウエハーの形状がゆがんだり反ったりし、膜にひび割れや空隙が生じ、欠陥や歩留まり低下を引き起こす。

VECTOR TEOS 3Dは厚く均一なダイ間のギャップ埋め込みに加え、独自の湾曲ウエハー搬送方法、プロセスを監視し再現性を持たせる「Lam Equipment Intelligence(ラム・エクイップメント・インテリジェンス)」 技術も採用。極めて厚く反りが大きいウェハーを安定して取り扱えるという。ナノスケールの精度でダイ間の埋め込みに特化した最大60μm厚の絶縁体膜を成膜でき、100μm超の膜厚にも対応。剥離などの課題を防ぐための構造や熱、機械的特性を提供できるとする。30μm超のクラックフリーな膜は歩留まりとプロセス時間を改善し、ウエハーを1枚ずつ処理する枚葉式の生産に資するという。

四つの独立したステーションでの並列処理が可能。同社の従来製品と比べ単位時間当たりの生産量を68%向上させ、ウエハー1枚当たりの処理費用など使用者コスト(COO)を最大20%改善できるとする。RF電源とECOモードによる付帯設備の制御でプロセス精度とエネルギー消費の削減の両立も図っている。

パイオニア 新体制で始動 次の成長への軌跡を追う

パイオニア 新体制で始動 次の成長への軌跡を追う