2024.12.05 半導体後工程の進化に貢献 25年4月からTSV/RDL受託開発・受託製造サービス開始

新サービスについて説明する平田会長

AI(人工知能)の普及拡大とともに、半導体の高性能化に向けた技術開発が加速している。半導体の高度化を実現するため、半導体製造における後工程の領域で技術革新が進む。後工程とは、半導体ウエハーへの回路形成を行う前工程に対し、ウエハーを切り分け、パッケージングを行い、半導体デバイスの形にする工程を指す。

高機能・高性能な半導体を作り込む技術として注目が集まっているのが、複数の異なる種類の半導体チップを1パッケージに収める「チップレット」と呼ばれる技術。複数の異種半導体チップを1パッケージに収めるためには、異種チップ間を接続するためのTSV(Through Silicon Via)と再配線層であるRDL(Redistribution Layer)が必須となる。

チップレットを実現するTSV/RDL技術

TSVとはシリコン貫通電極のことで、従来のワイヤを用いた接続方法と異なり、チップに微細な穴を開け上下のチップを電極で接続する技術。RDLはデバイス内部に配線を再分配するための層を形成する技術で、これら二つの技術ともチップレットには不可欠な技術だ。チップレット市場の伸長に伴い、TSV/RDLを用いた半導体市場規模は、年間1兆円以上と推定され、今後も大きな成長が期待されている。

急速な技術革新と開発が進むチップレットだが、大きな課題がある。それは、供給面の課題だ。TSV/RDLを必要とする半導体に対し、開発の初期段階から生産まで一貫して委託できる企業は少ない。TSV/RDLを受託する海外ファウンドリーは存在するものの、開発初期段階で必要となる短期間での少量試作や品質保証を伴う量産に対応できる企業は限られている。

TSV/RDLの受託開発・受託製造サービスを25年4月から開始

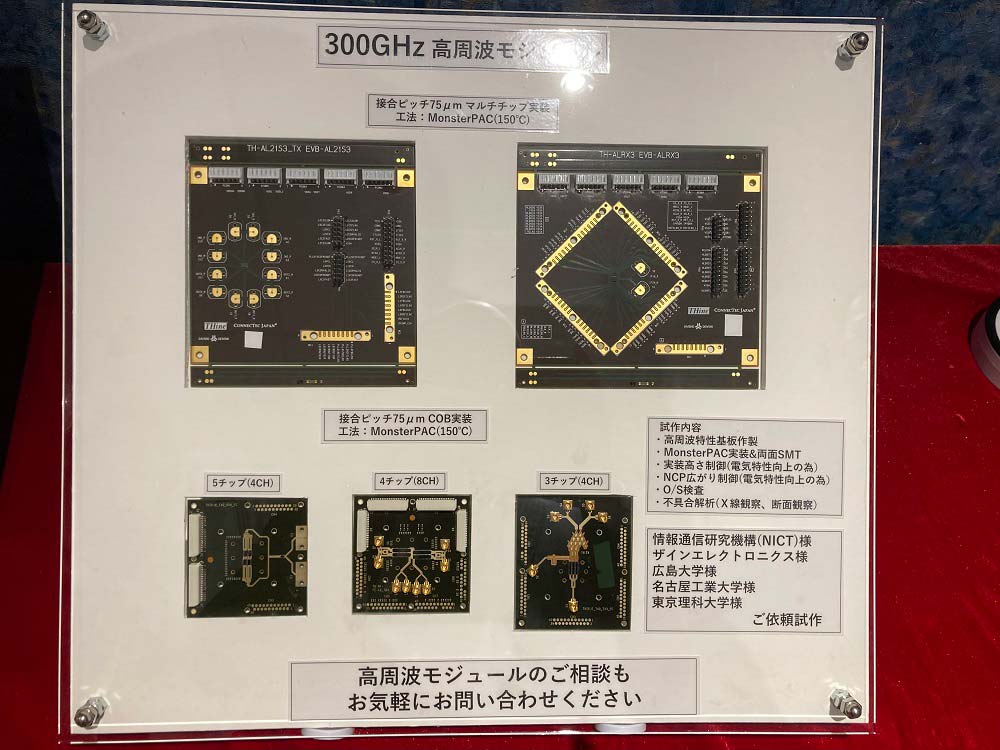

この大きな課題に対応するのが、新潟県妙高市に本社を構えるコネクテックジャパンだ。同社は、半導体をはじめ、センサーやMEMSの実装受託開発・受託製造サービスを提供している。低温から高温まで幅広い接合技術を有し、年間400件におよぶ半導体実装受託開発と製造の実績を持つ。

同社は最先端のチップレット実現に向け、2025年4月からTSV/RDLの受託開発、受託製造サービスを開始する。供給面の課題を解決するとともに、これまで培ってきた高い技術力とノウハウにより技術面の課題解決にも貢献する。

平田勝則会長は「生成AIの普及拡大には、最先端のチップレット技術が必要。TSV/RDLの実装受託開発および受託製造の一気通貫サービスにより、先端パッケージングの技術革新に貢献する」と話す。

高い技術力で技術課題も解決

TSV/RDLの技術面での課題は、ビアの小径化と再配線層の多層化。SoC(System on Chip)のチップ内部が数ナノメートルのビアと10層以上の配線で構成されるのに対し、現状のTSV/RDLは直径10マイクロメートルのビア、1~2層配線となっている。SoCでは、チップ内で最短接続できる配線をチップレットパッケージでは一旦チップ外でTSVとRDLを用い接続するため、配線を駆動する消費電力が増加する。AIデータセンターの消費電力増加が問題となる中、SoCの微細化と同様にパッケージレベルでの配線の最短化、高密度化を実現するため、TSV/RDLのさらなる小径化と多層化が必須となる。

今後のロードマップとして、25年第2四半期(4~6月)に月産20枚(ウエハーサイズ200㍉㍍)体制でのTSV/RDL受託開発を開始。TSV径20マイクロメートル、RDL層数は1層でスタートする。26年第2四半期には少・中量生産を開始し、月産300枚(ウエハーサイズ300㍉㍍)、TSV径10マイクロメートル以下、RDL層数は2層に引き上げる。27年第2四半期には中・大量生産を開始し、月産1000枚(ウエハーサイズ300㍉㍍)、TSV径1マイクロメートル、RDL層数は4層にする計画だ。

平田会長は「着実な設備投資を計画しており、新たな工場の建設も視野に入れる。本社のある新潟だけでなく、地の利を生かせる最適な場所を検討したい」と話す。

今回の事業計画推進では、産業技術総合研究所九州センターなど、TSV/RDL技術を有する国内研究機関・技術保有企業と連携し、事業化を進めている。今後大きな成長が期待されるチップレットの課題解決に貢献し、半導体の技術革新を後押しする。