2022.07.28 【半導体/エレクトロニクス商社特集】3D実装/パッケージング微細化の限界を超える日本企業にも商機

インテルのパッケ-ジング開発拠点であるリオランチョの工場

半導体の高性能化を実現してきた微細化のペースがスローダウンするとともに、チップを垂直方向に積み重ね性能向上を図る3次元(3D)実装などの技術開発が活発化してきた。台湾TSMCや米インテルなど、ロジックの前工程分野をリードしてきた企業も投資を拡大し、集積技術や先端パッケージング技術開発を競っている。

近年、注目を集めているのは「チップレット」と呼ばれる2Dの混載技術。CPUやGPU、SRAMなどそれぞれ最適なプロセスノードや装置で製造されたチップ(チップレット)をブロックのように組み合わせ、1枚のインターポーザー上に配置、SoP(システム・オン・パッケージ)技術で1パッケージに収納する。これにより微細化に頼らず半導体の小型化や機能向上を実現。各チップレットのサイズを小さくできるため歩留まりも向上し、市場投入までの期間を短縮できる。

米AMDは、これをパソコン用CPU「Ryzen」やサーバー用「EPYC」にいち早く採用。モノリシックダイを採用する米インテルの競合プロセッサーを性能で上回り、AMD躍進のきっかけをつくった。AMDはその後CPUダイにSRAMを縦方向に積層した「3Dチップレット」技術も開発し、CPUの性能の大幅向上を図っている。

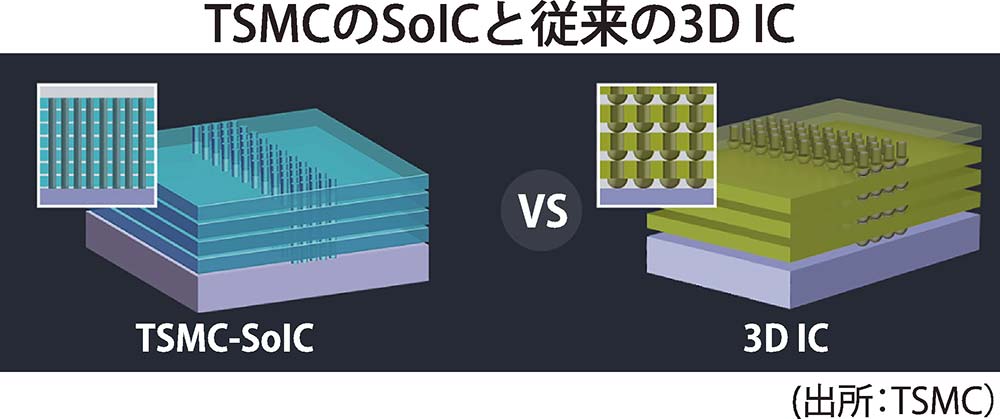

AMDのチップは台湾TSMCが製造する。TSMCは半導体製造の前工程のリーダー企業だが、パッケージング技術にも長年注力してきた。2D混載技術「CoWoS(コワス)」や「InFO(インテグレーテッド・ファンアウト)」などを提供するほか、これらと組み合わせる3D実装技術「SoIC(システムオン・インテグレーテッド・チップ)」(図参照)も開発している。

TSMCは、こうした2Dや3Dパッケージング技術を研究する施設「TSMCジャパン3DIC研究センター」を茨城県つくば市に今年6月に開設した。同社にとっては台湾以外の国に設置される最初の研究施設だ。

オープニング式典であいさつしたセンター長の江本裕氏は「サブストレートなどの素材メーカーや製造装置メーカーが集中しており、研究する上でそうしたメーカーと迅速にやりとりできる」と日本に研究施設を置くメリットを説明した。

同センターは半導体産業復活を図る日本政府肝いりのプロジェクトであり世界からの注目度も高い。日本の素材・装置メーカーには大きな商機となる。

パッケージング技術にはインテルや韓国サムスン電子も本格的に取り組む。「EMIB」や「Foveros」などの高密度実装技術を有するインテルは昨年来、パッケージング強化に向けニューメキシコ州リオランチョ工場やマレーシア工場への投資を拡大。また欧州でもパッケージの拠点を開設する計画だ。

先端半導体での主導権争いは激しさを増すが、業界リーダー企業らがそろって口にするのはパートナー企業との協業の重要性だ。

先のチップレットに関しては今年5月、チップレット間相互接続のためのオープン規格「UCIe1.0」を推進する業界団体が設立され、パッケージング大手の台湾ASEやAMD、インテル、サムスン、TSCMほかマイクロソフトなど米IT大手が参加した。垣根を超えチップセットの普及促進を図り、半導体の高性能化を加速させるのが目的だ。これら企業間での技術の擦り合わせにも、部材に強みを持つ日本企業が重要な役割を担うと期待されている。

後工程分野特化の国際展示会、SEMIが12月に都内で開催

SEMI(半導体製造装置材料協会)ジャパンは、半導体パッケージング・実装技術など注目が集まる後工程分野に特化した国際展示会「APCS:アドバンスド・パッケージング・アンド・チップレットサミット」を12月に東京都内で開催する。「2.5D/3Dチップレット」や「ヘテロジーニアス(異種混合)接合」「TSV」「RDL(再配線層)」などの新技術や最新の半導体設計手法、シミュレーションツールなどを紹介する。会期は12月14~16日。会場は東京ビッグサイト(東京都江東区)。半導体関連の国際展示会「SEMICOn Japan」との同時開催となる。

開催に向けては、長瀬産業や昭和電工マテリアルズなどパッケージング分野の大手企業10社と大学が「APXCS実行推進委員会」を設立した。