2025.10.24 仏半導体新興、AI推論用チップをテープアウト メモリー設計刷新で電力50%減

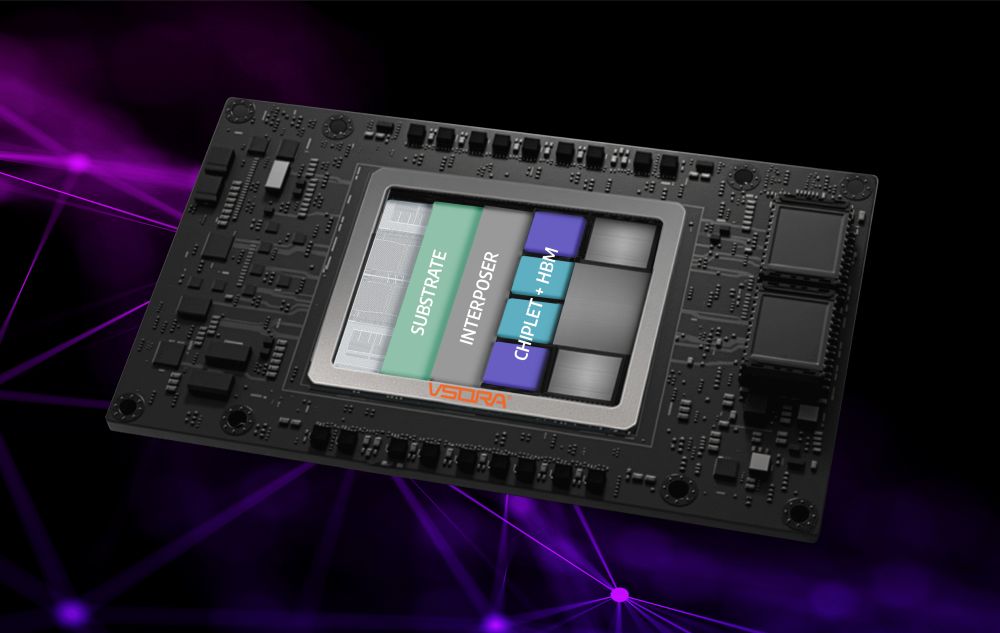

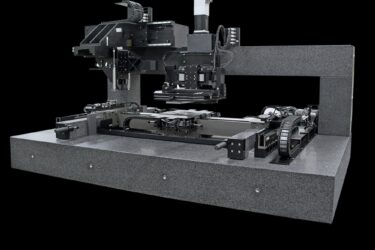

テープアウトしたJotunn8-3D

仏半導体スタートアップでファブレスのVSORAは、AI(人工知能)推論向けチップ「Jotunn8」のテープアウトに成功したと発表した。設計が完了し製造の段階に入る。製造開発ボード、リファレンスデザイン、サーバーが2026年初頭に発売される本格的な展開を想定し、準備を進める。

Jotunn8は、プロセッサーの演算速度に対してメモリーへのデータ伝送が追いついておらず、速度や消費電力の面でボトルネックを抱えていたというAIチップの課題に対応する。キャッシュメモリーなど、従来の階層構造を持ったメモリーにアクセスする方法ではなく、それらを回路内部にあるレジスタ群に統合するアーキテクチャーだ。

製造では、TSMC(台湾積体電路製造)の5nm プロセスと、中間基板を挟んで複数のチップを1パッケージに統合する最先端の CoWoS マルチチップ パッケージ技術を活用する。TSMCを筆頭株主とする設計支援会社GUC(グローバル・ユニチップ)の協力を得た。

HBM(広帯域幅メモリー)で「3e」と呼ばれる世代のものを288GB搭載し、3200 Tflops(1秒間で3200兆回の計算)の性能を持つ。市場をリードする既存チップから消費電力を半減できるという。

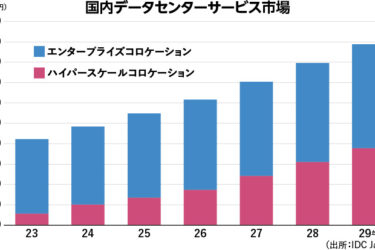

用途はデータセンター向けのAI推論を想定。同社は、この分野に取り組むヨーロッパで唯一の企業だとうたう。