2022.10.28 【半導体製造装置特集】半導体需要拡大で製造装置好調、日本製製造装置が世界をけん引

需要増に対応した設備増強で半導体製造装置の需要も拡大している

半導体の市場拡大に伴い、半導体製造装置も半導体サプライヤーの旺盛な設備投資に支えられて需要増が続いている。微細化、3DIC、新パッケージングなど半導体製造プロセスの進化に伴い、半導体製造装置も技術革新が続く。

半導体の世界需要

世界の主要半導体関連企業が加盟する統計機関WSTS(世界半導体市場統計)は、6月の時点の2022年の世界半導体市場見通しをメモリーの需要の減速などから8月に下方修正したが、それでも6332億ドル、前年比13.9%増と2桁成長を予測する。ウクライナ危機などマイナス要因はあるが、経済活動の正常化、設備投資の拡大傾向、EV化をはじめとする脱炭素化の潮流などが半導体需要を押し上げる。

半導体製造装置の動向

半導体の市場拡大に伴い半導体製造装置の需要も増加している。

SEMIは、22年の世界の半導体製造装置販売額は前年比14.7%増の1175億ドルになるとの見通しを7月に発表した。23年は伸びは鈍化するものの、同2.8%増の1208億ドルを見込んでおり、4年連続で過去最高を更新する見込み。地域別には台湾、韓国、中国が中心となるが、欧州/中東、南北アメリカ、東南アジアも過去最高を記録する見込み。

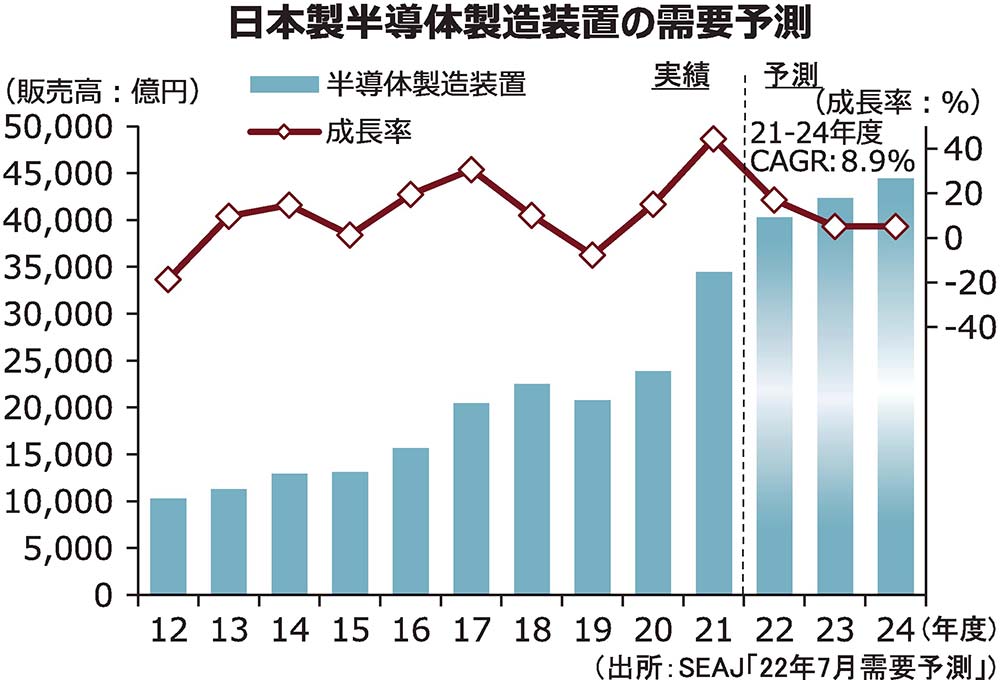

日本製装置の販売が好調推移

日本製半導体製造装置が世界をけん引している。SEAJ(日本半導体製造装置協会)によると、22年度(4月~23年3月)の日本製装置販売高は、ロジック・ファウンドリーの積極投資に加えて、メモリー全般で高水準の投資が増加していることで前年度比17.0%増、4兆283億円、23年度は同5.0%増、4兆2297億円を見込む。

このうち日本市場での販売高は、22年度は同30.0%増、1兆1834億円、23年度は同10.0%増、1兆3017億円の予想となっている。

FPD製造装置は、22年度同0.9%増、4850億円、23年度は同7.2%減、4500億円を見込む。

設備投資動向

22年以降に生産増強や新たに量産を開始する半導体サプライヤーのプロジェクトは、世界で150以上動いていると言われる。ロジックやファウンドリーの積極投資や、DRAMの新規格DDR5の本格的な移行に向けたFPD投資など最先端のみならず、供給不足を補うレガシー半導体への投資も活発。

米インテルは、オハイオ州で今後10年で1000億ドル規模の投資を行い、計8棟のファブを擁する巨大半導体製造拠点を整備する。欧州でも研究開発/製造について今後、10年間で800億ユーロを投資する。韓国サムスン電子は、今後20年以内に米テキサス州に11の新しい半導体工場を建設するプロジェクトをスタートした。また、ソウル近郊の半導体主力拠点に新製造棟を建設し、投資額は2兆円を上回る見通し。

半導体受託生産で世界最大手の台湾TSMCは、22年の設備投資額が440億ドルに達する。熊本にも新工場を設けるほか、2ナノメートル製品を生産する新工場を台湾に建設。中国のファウンドリー最大手SMICは、億ドルを投じて天津市に半導体工場を新設する。完工時期は明らかにしていないが、28ナノメートル製品の生産が主になると見られている。

注目される3D実装とチップレットプロセス

半導体プロセスの進化

物理的限界に近づく微細化技術

これまではチップ上に描く(露光する)回路の線幅を小さくして集積度を高める前工程の微細化技術は、最先端では韓国サムスン電子とTSMCが3ナノメートルプロセス技術を確立している。

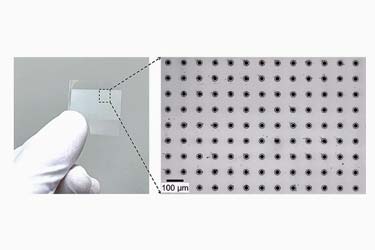

しかし、微細化は物理的にも限界に近づいているため、高機能化や多機能化を継続していくために後工程の重要性が高まり、その一つのプロセスとして3D(3次元)または2.5D(2.5次元)実装技術が注目されている。

同技術はシリコンウエハー上で電子回路を形成し、薄片化した半導体ウエハーを3Dに積層化して、層間を貫通電極を使って通電させるため、半導体の小型化/高密度化/省電力化、さらに信号伝送と処理速度の高速化など、数多くのメリットが生まれる。具体的には、演算を行うロジックチップとメモリー、アナログデバイス・センサーなどを一つのパッケージに統合する。

最初の積層技術として登場したTSV(シリコン貫通ビア)は、3Dスタックメモリー、GPU、FPGA、CMOSイメージセンサーなど、さまざまな半導体デバイスで活用されるようになっている。

もう一つ注目されている製造プロセスが、「チップレット」と呼ばれる2Dの混載技術。CPUやGPU、SRAMなど、それぞれ最適なプロセスノードや装置で製造されたチップをブロック玩具のように組み合わせ、1枚のインターポーザー上に配置して、SoP(システム・オン・パッケージ)技術で1パッケージに収納する。

これにより、微細化に頼らず半導体の小型化や機能向上を実現。各チップのサイズを小さくできるため歩留まりも向上し、市場投入までの期間を短縮できる。CPUダイにSRAMを縦方向に積層した「3Dチップレット」技術も開発されている。

3DICやチップレットプロセスはボンディング装置や、はんだボールマウンティング装置などの装置需要を拡大し、またSMTプロセスとの融合も進むことになる。