2025.01.06 東レエンジニアリング 2.5/3Dパッケージを実現するガラス基板向け装置を開発

パネルレベル塗布装置「TRENG-PLPコーター」

半導体の高度化を実現するため、半導体製造における後工程の領域で技術革新が進む。後工程とは、半導体ウエハーへの回路形成を行う前工程に対し、ウエハーを切り分け、パッケージング、電極形成を行い、半導体デバイスの形にする工程を指す。高機能・高性能な半導体を作り込むため、さまざまな技術が開発されているが、その一つとして近年、注目を集めているのがチップを積層化する「2.5/3次元(2.5D/3D)実装)」。従来はパッケージ基板にチップを実装し、樹脂封止(パッケージング)することで、半導体デバイスとして完成していた。これらを2次元(2D)パッケージと呼ぶのに対し、異なる種類のデバイスを複数配置し、異種チップ同士を接続するために中継部材である「インターポーザー」に実装することでチップを積層化する。現在は3D実装を見据えた開発が進められているものの、技術的に到達しておらず、まずは2.5D、2.xDを用いた技術開発が進んでいる。この2.5D/3D実装を実現するために必要となるインターポーザー製造のための製造装置も開発されている。

東レエンジニアリング(TRENG)は昨年末、先進パッケージ向けパネルレベル塗布装置「TRENG-PLPコーター」を開発した。同装置は、2.5/3Dパッケージ向け大型インターポーザーの製造に対応するもの。スリットノズルで再配線層の素材を塗布し、真空・加熱乾燥までを一貫して行う。高い塗布性能や多種多様な薬液・大型基板に対応するなどの特徴を持ち、インターポーザーの素材であるガラス基板上に微細な再配線層を形成し、2.5/3D実装を実現する。同製品は昨年12月11日から受注を開始しており、2025年度に30億円、30 年度には60 億円の受注を目指す。

インターポーザーは従来、シリコン素材で製造されていたが、円形の300ミリメートルウエハーから角型に切り出して製造するとデッドスペースが生まれ、製造効率の低下につながる。また、半導体の高性能化に伴い、パッケージサイズも年々大型化。製造効率がさらに低下していくことが懸念されており、インターポーザーにもさらなる大型化が求められていた。パッケージの大型化とともにインターポーザーの反りも問題となっており、シリコンよりも強度がある角型のガラス基板を用いたインターポーザーが注目されるようになった。このガラスインターポーザーを用いたパッケージは「パネルレベルパッケージ(PLP)」と呼ばれ、技術開発が進んでいる。

ガラス基板は600×600ミリメートルと、ウエハーに比べて大型化が可能。角型のため、基板の隅まで有効活用できる。ガラス基板の反りを制御し、配線材料やフォトレジスト材の薄さを均一に保ち、高密度に回路を形成することが課題となる。これらの課題に対して、同社は保有する液晶パネル向けに展開してきた高精度に厚みをコントロールするコーティング技術、大型ガラス基板のハンドリング技術を展開することで、同装置で600×600ミリメートルのガラス基板上に高密度な再配線層の形成を実現した。

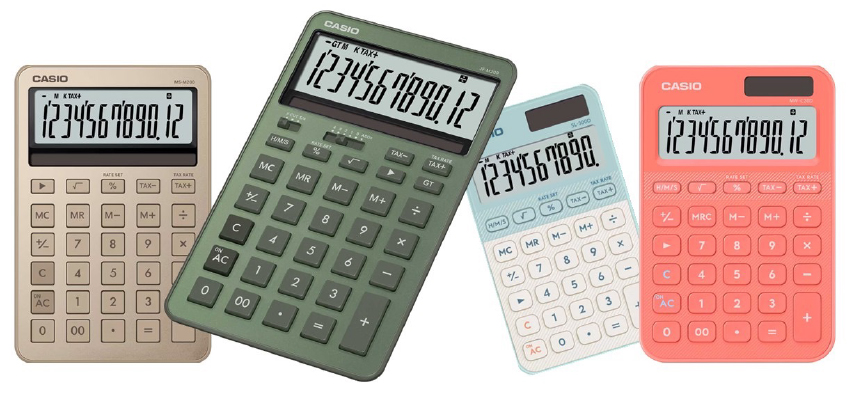

カシオ計算機 8年ぶりの刷新 デザイン電卓15色登場

カシオ計算機 8年ぶりの刷新 デザイン電卓15色登場