2023.03.23 計算速度スパコンの10万倍、量子計算機実用化へ新技術 富士通と阪大、高精度に量子エラー訂正

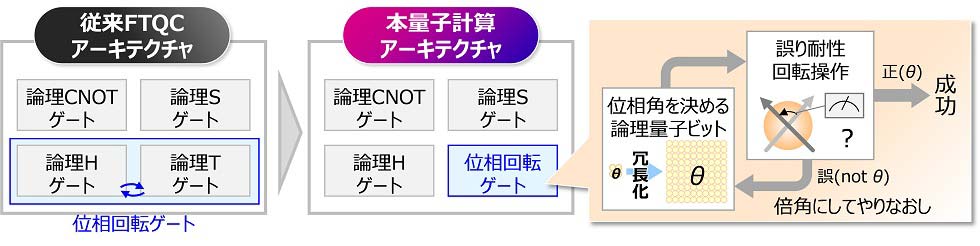

富士通と大阪大が確立した量子計算アーキテクチャのイメージ

量子コンピューティングの欠点だった「量子エラー訂正」を高精度に行い、現行のスーパーコンピューターの10万倍相当の計算性能を発揮できる量子計算アーキテクチャを富士通と大阪大学が確立した。実現は10~20年後とされていた技術が大幅に短縮される可能性があり、量子コンピューターの早期実用化が期待される。

両者が確立したのは、量子エラー訂正に必要な物理量子ビット数を大幅に低減することで、計算能力を高める高効率位相回転ゲート式量子計算アーキテクチャ。

量子計算に使われる量子ビットは、0か1かのビットで情報を処理する従来のコンピューターに対し、0と1の両方が同時に存在する「重ね合わせ」などで情報を管理する。だが、重ね合わせの状態は熱などの外部環境や操作信号などノイズの影響で非常に壊れやすく、複雑な計算をしようとするとエラーが発生するため、正確な結果が得にくい欠点がある。この課題の克服に必要となるのが、誤りを制御する量子エラー訂正技術だ。

今回確立したのは、物理量子ビットを使用する論理ゲート操作を繰り返す従来のアーキテクチャとは異なり、任意の角度を直接指定して、量子計算に含まれる状態ベクトルの向き(位相)を回転させる操作を行う。これまではこの位相回転を平均50回程度繰り返す必要があったが、論理量子ビットで正しく関連するまで位相回転をやり直すことで2回程度のトライアルで回転が完了。物理量子ビットを従来の10分の1以下に低減し、任意回転の実行に掛かるゲート操作回数も従来の20分の1程度に減らすことができた。量子エラー確率は、物理量子ビットでの量子エラー確率の約8分の1まで抑え込め、高精度な計算ができることを確認した。

これにより1万物理量子ビットに対して64論理量子ビットの量子コンピューターが構築でき、計算性能は現行最高性能のコンピューターの約10万倍に相当すると見込まれている。

(27日付の電波新聞/電波新聞デジタルで詳報します)